# DESCRIPTION

The MPQ6400 family is the microprocessor (µP) supervisory circu it which can monitor and provide reset function for system voltages from 0.4V. Whe n either the SENSE voltage falls below its t hreshold ( $V_{IT}$ ) or the voltage of manual reset (MR) is pulled to a logic low, the RESET signal will be a sserted. The r eset voltage can be factory-set for standard voltage rails from 0. 9V to 5V, while the MPQ6400DG-01 reset voltage is adju stable with an external resistor divider. When SENSE volt age and MR exceed their thresholds, RESET is driven to a after a user-programmable delay logic high time.

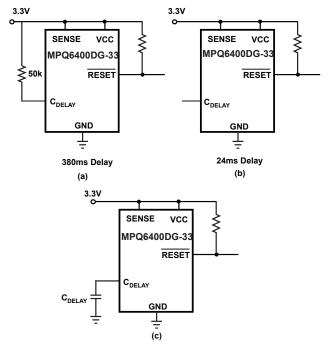

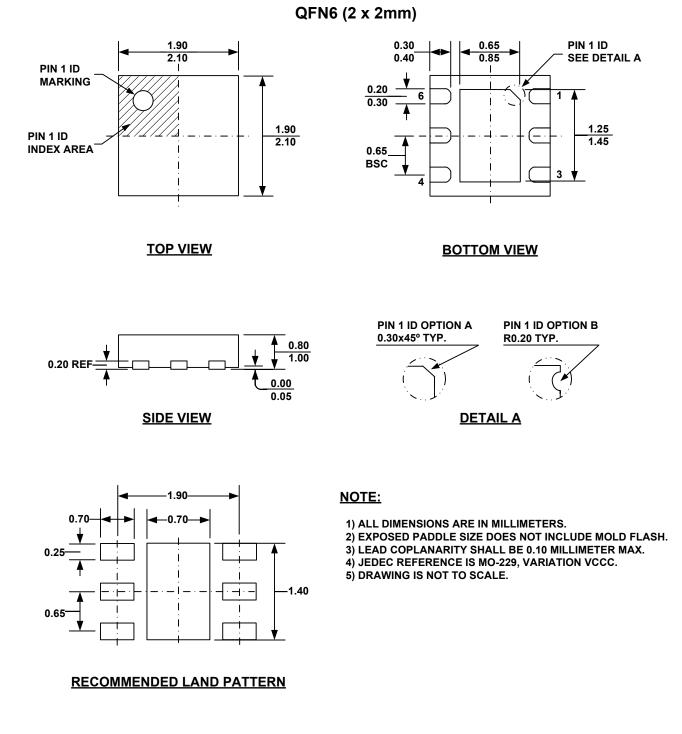

The MPQ6400 has a very low quiescent current of 1.6µA typically, which makes it ideal suitable for battery-powered application s. It provides a precision re ference to achieve  $\pm 1\%$  threshold accuracy. The reset delay time can be select ed by a capacitor which is connect ed between C<sub>DELAY</sub> and GND, allowing the user to select any delay time from 2.1ms to 10s. 380ms delay time is selected by connecting the C<sub>DELAY</sub> pin to V<sub>CC</sub>, while 24ms delay time by leaving the C<sub>DELAY</sub> pin float. MPQ6400 is available in 2mm×2mm 6-pin QFN package.

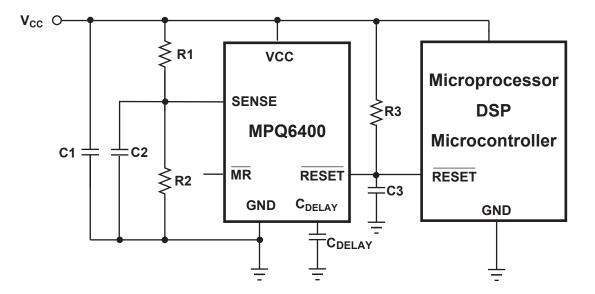

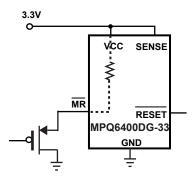

## **TYPICAL APPLICATION**

## FEATURES

- Guaranteed Industrial/Automotive Temp Range Limits

- Fixed Threshold Voltages for Standard Voltage Rails From 0.9V to 5V and Adjustable Voltage From 0.4V are Available

- Low Quiescent Current: 1.6µA Typ

- Power-On Reset Generator with Adjustable Delay Time: 2.1ms to 10s

- High Threshold Accuracy: ±1% Typ

- Manual Reset (MR) Input

- Open-Drain RESET Output

- Immune to Short Negative SENSE Voltage

- Guaranteed Reset Valid to V<sub>CC</sub>=0.8V

- 2×2mm QFN

## APPLICATIONS

- DSP or Micro controller Applications

- Laptop/Desktop Computers

- PDAs/Hand-Held Products

- Portable/Battery-Powere d Products

- FPGA/ASIC Applications

For MPS green status, please visit MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

## **ORDERING INFORMATION**

| Part Number* Package |              | TJ              |

|----------------------|--------------|-----------------|

| MPQ6400DG-33**       | QFN6 (2x2mm) | -40°C to +125°C |

| MPQ6400DG-33-AEC1    | QFN6 (2x2mm) | -40°C to +125°C |

\*For Tape & Reel, add suffix –Z (e.g. MPQ6400DG–XX-Z); For RoHS compliant packaging, add suffix –LF (e.g. MPQ6400DG–XX-LF–Z).

\*\* Check factory for availability in other options.

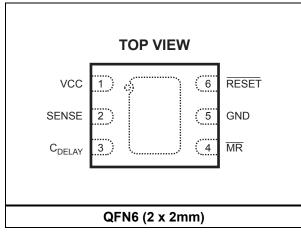

## PACKAGE REFERENCE

## ABSOLUTE MAXIMUM RATINGS (1)

| $\begin{array}{l} Supply \mbox{ Voltage } V_{CC} \hfill \\ C_{DELAY} \mbox{ Voltage } V_{CDELAY} \hfill \\ SENSE \mbox{ Voltage } V_{SENSE} \hfill \\ All \mbox{ Other Pins} \hfill \\ RESET \mbox{ Current } I_{RESET} \hfill \\ \end{array}$ | .3V to V <sub>CC</sub> + 0.3V<br>0.3V to 6V<br>0.3V to +6.0V      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Continuous Power Dissipation<br>QFN6 (2mmx2mm)<br>Junction Temperature<br>Lead Temperature<br>Storage Temperature                                                                                                                              | (T <sub>A</sub> = +25°C) <sup>(2)</sup><br>2.5W<br>150°C<br>260°C |

## Recommended Operating Conditions <sup>(3)</sup>

| Supply Voltage V <sub>CC</sub> . |                         | 1.8V | to 5.5V |

|----------------------------------|-------------------------|------|---------|

| Maximum Junction 7               | Гетр. (Т <sub>Ј</sub> ) |      | +125°C  |

## **Thermal Resistance** <sup>(4)</sup> **θ**<sub>JA</sub> **θ**<sub>JC</sub> QFN6 (2x2mm) ......50 ...... 12...°C/W

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature r T J(MAX), the junction-to-ambient thermal resistance θ<sub>JA</sub>, and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub>(MAX)=(T<sub>J</sub>(MAX)-T<sub>A</sub>)/θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Inter rnal thermal shutdo wn circuitr y protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7 4-layer board.

# **ELECTRICAL CHARACTERISTICS**

1.8V≤V<sub>CC</sub>≤5.5V, R<sub>3</sub> = 100k $\Omega$ , C<sub>3</sub> = 47pF, T<sub>J</sub>= -40°C to +125°C, Typical values are at T<sub>j</sub>=+25°C, unless otherwise noted.

| Parameters Sy                                 | mbol                | Condition                                                                                         | Min                | Тур  | Мах                 | Units             |

|-----------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------|--------------------|------|---------------------|-------------------|

| Input Supply Range                            | Vcc                 |                                                                                                   | 1.8                |      | 5.5                 | V                 |

| Supply Current                                | I <sub>CC</sub>     | $V_{CC}$ = 3.3V, RESET not<br>asserted. MR, RESET,<br>$C_{DELAY}$ open                            | 1.6                |      | 5                   | μΑ                |

| (current into V <sub>CC</sub> pin)            | ICC                 | $V_{CC}$ = 5.5V, RESET not<br>asserted. MR, RESET, C <sub>DELAY</sub><br>open                     | 1.85               | 1    | 5                   | μΑ                |

| Low-level Output Voltage                      |                     | $1.3V \le V_{CC} < 1.8V,$<br>$I_{OL} = 0.4mA$                                                     |                    |      | 0.3                 | V                 |

|                                               | V <sub>OL</sub>     | $1.8V \le V_{CC} \le 5.5V$ ,<br>$I_{OL} = 1.0mA$                                                  |                    |      | 0.4                 | V                 |

| Power-up Reset Voltage <sup>(5)</sup>         |                     | V <sub>OL</sub> (max) = 0.2V,<br>I <sub>RESET</sub> = 15uA<br>T <sub>rise(Vcc)</sub> ≥15µs/V      |                    |      | 0.8                 | V                 |

| Negative-going Input Threshold                | N/                  | -40°C to +85°C                                                                                    | -2.5               | ±1.0 | 1.5                 | 0/                |

| Accuracy <sup>(7)</sup>                       | V <sub>IT</sub>     | -40°C to +125°C                                                                                   | -3                 |      | 1.7                 | %                 |

| Hysteresis on V <sub>IT</sub> Pin             | $V_{\text{HYS}}$    |                                                                                                   |                    | 1.5  | 4                   | V <sub>IT</sub> % |

| MR Internal Pull-up Resistance                | $R_{\overline{MR}}$ | 50                                                                                                |                    | 110  |                     | kΩ                |

| Input Current at SENSE Pin                    | I <sub>SENSE</sub>  | Fixed versions<br>V <sub>SENSE</sub> = 6V                                                         | 2.4                |      |                     | μA                |

| RESET Leakage Current                         |                     | $V_{\overline{\text{RESET}}}$ = 5.5V, $\overline{\text{RESET}}$ not asserted                      |                    |      | 500                 | nA                |

| MR Logic Low Input                            | VIL                 |                                                                                                   |                    |      | 0.25V <sub>CC</sub> | V                 |

| MR Logic High Input                           | V <sub>IH</sub>     |                                                                                                   | 0.7V <sub>CC</sub> |      |                     | V                 |

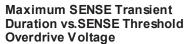

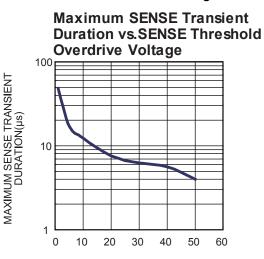

| SENSE Maximum Transient Duration              | t <sub>w</sub>      | V <sub>IH</sub> = 1.05 V <sub>IT</sub> ,<br>V <sub>IL</sub> = 0.95 V <sub>IT</sub>                | 17.5               |      |                     | μs                |

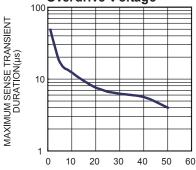

|                                               |                     | C <sub>DELAY</sub> = Open                                                                         | 15                 | 24   | 34                  | ms                |

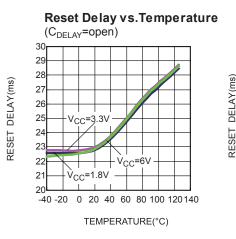

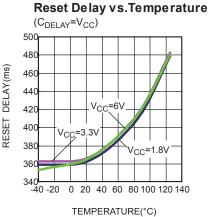

|                                               | t <sub>d</sub>      | $C_{\text{DELAY}} = V_{\text{CC}}^{(6)}$                                                          | 230                | 380  | 530                 | ms                |

| RESET Delay Time                              | La                  | $C_{\text{DELAY}} = 150 \text{pF}$                                                                | 1.3                | 2.1  | 3                   | ms                |

|                                               |                     | $C_{\text{DELAY}} = 10 n F^{(6)}$                                                                 | 61                 | 102  | 142                 | ms                |

| MR to RESET Propagation Delay                 | $t_{\text{pHL1}}$   | $V_{\text{IH}} = 0.7 V_{\text{CC}},$<br>$V_{\text{IL}} = 0.25 V_{\text{CC}}$                      | 160                |      |                     | ns                |

| High to Low Level RESET Delay, SENSE to RESET | t <sub>pHL2</sub>   | $\label{eq:VIH} \begin{array}{l} V_{IH} = 1.05 \; V_{IT}, \\ V_{IL} = 0.95 \; V_{IT} \end{array}$ | 17.5               |      |                     | μs                |

Note:

5) The lowest supply voltage ( $V_{cc}$ ) at which RESET becomes active.

6) Guaranteed by design.

7) V<sub>SENSE</sub> Falling Slowly

## **ORDERING INFORMATION**

| Product      | Package | Top Mark | Nominal Supply Voltage | Threshold Voltage (VIT) |

|--------------|---------|----------|------------------------|-------------------------|

| MPQ6400DG-33 | QFN     |          | 3.3V                   | 3.07V                   |

## **PIN FUNCTIONS**

| QFN<br>Pin # | Name D             | es cription                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 V          | CC                 | Supply voltage. A 0.1uF decoupling ceramic capacitor should be put close to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2 SEI        | NSE                | SENSE pin is connected to the monitored system voltage. When the monitored voltage is below desired threshold, $\overline{\text{RESET}}$ is asserted.                                                                                                                                                                                                                                                                                                                                                             |

| 3            | C <sub>DELAY</sub> | Programmable re set del ay time pin. Whe n C <sub>DELAY</sub> c onnected to V <sub>CC</sub> throug h a re sistor between 50k $\Omega$ and 200k $\Omega$ , a 380ms de lay time is selected. Wh en C <sub>DELAY</sub> floated, the delay time is 24ms. A capacitor bigger than 150pF connected C <sub>DELAY</sub> to GND could be used to get the user's programmable time from 2.1ms to 10s.                                                                                                                       |

| 4            | MR                 | The manual reset ( $\overline{\text{MR}}$ ) can introdu ce a nother lo gic signal to control the $\overline{\text{RESET}}$ . It is internally connected to V <sub>CC</sub> through a 90k $\Omega$ resistor.                                                                                                                                                                                                                                                                                                       |

| 5            | GND                | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6            | RESET              | $\overrightarrow{RESET}$ is an open drain signal which will be asserted when the SENSE voltage drops below<br>a preset threshold or when the manual reset ( $\overrightarrow{MR}$ ) pin drops to a logic low. The $\overrightarrow{RESET}$ delay<br>time is programmable from 2.1ms to 10s by using external cap acitors. A pull-up re sistor<br>bigger than 10k should be connected this pin to su pply line, and the $\overrightarrow{RESET}$ outputting a<br>higher voltage than V <sub>CC</sub> is allowable. |

## **DETAIL DESCRIPTION**

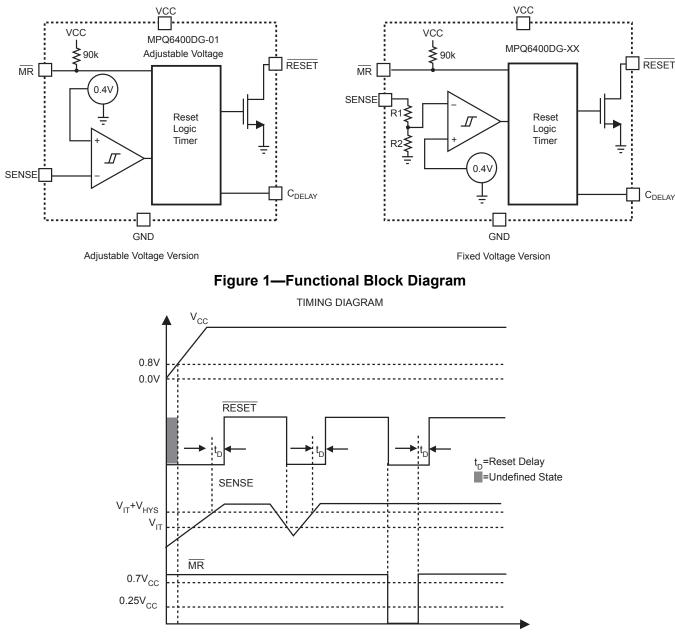

The MPQ6400 product fam ily asserts a RESET signal whe n either the SENSE pin voltage is lower than V<sub>IT</sub> or the manual reset ( $\overline{MR}$ ) is driven low. The MPQ6400-XX fa mily, o ther than the MPQ6400DG-01, can monitor a fixed voltage from 0.9V to 5.0 V. The MPQ6400DG-01 can monitor any voltage above 0.4V by adjusting the external resistor divider. After both the manual reset ( $\overline{MR}$ ) and SENSE voltages exceed their thresholds, the RESET

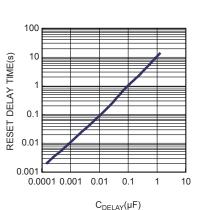

output re mains asserted for a user 's programmable delay time. Two fixed  $\overrightarrow{RESET}$  delay times are user-selectable: 380m s d elay time by connecting the C<sub>DELAY</sub> pin to V<sub>CC</sub>, and 24ms delay time by leaving the C<sub>DELAY</sub> pin floa t. Any delay time from 2.1ms to 10s could b e gotten by connecting a capacitor between C<sub>DELAY</sub> and GND. The wide m onitor voltage and p rogrammable reset delay time make MPQ6400 product fam ily suitable for a broad array of applications.

Reset Delay Time vs. CDELAY

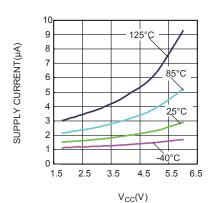

## TYPICAL PERFORMANCE CHARACTERISTICS

$V_{CC}$ =3.3V,  $R_3$  = 100k $\Omega$ ,  $C_3$  = 47pF,  $T_A$ = -40°C to +125°C, Typical values are at  $T_A$ =+25°C, unless otherwise noted.

Supply Current vs. V<sub>CC</sub>

SENSE THRESHOLD OVERDRIVE(%)

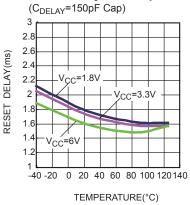

Reset Delay vs.Temperature

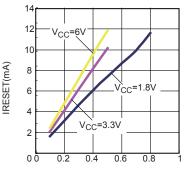

**IRESET VS. LOW LEVEL Reset Voltage**

LOW LEVEL RESET VOLTAGE(V)

Temperature 0.2 0.1 V<sub>CC</sub>=1.8V 0 -0.1 -0.2 V<sub>CC</sub>=́6V -0.3 -0.4 V<sub>CC</sub>=3.́3\ -0.5 -0.6 0 20 40 60 80 100 120 140

TEMPERATURE(°C)

VORMALIZED VIT (%)

-40 -20

Normalized VIT vs.

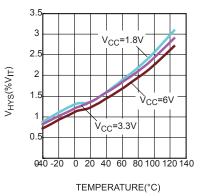

## V<sub>HYS</sub> vs. Temperature

MPQ6400 Rev. 1.0 www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 12/5/2011 © 2011 MPS. All Rights Reserved.

## FUNCTIONAL BLOCK DIAGRAM

Time

| MR | SENSE > V <sub>IT</sub> | RESET |  |

|----|-------------------------|-------|--|

| L  | 0                       | L     |  |

| L  | 1                       | L     |  |

| Н  | 0                       | L     |  |

| Н  | 1                       | Н     |  |

#### **TRUTH TABLE**

## **APPLICATION INFORMATION**

### **Reset Output Function**

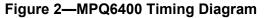

The M PQ6400 RESET output is typically connected to the  $\overline{RESET}$  input of a microprocessor, as shown in Figure 3. When RESET is not asserted, a pull up resistor must be connected to hold this signal high. The voltage of reset signa I is allowed to be high er than V  $_{CC}$  (up to 6 V) through a r esistor pulling up from supply line. If the voltage is below 0.8V, **RESET** Output is undefined. This co ndition ca n be ign ored generally because that most microprocessors do not function at this state. When both SENSE and MR are higher than their threshold voltage, RESET output hold s logic high . Once eith er of the tw o drops belo w their th reshold, RESET will be asserted.

### Figure 3—Typical Application of MPQ6400 with Microprocessor

From the p oint that  $\overline{MR}$  is again logic high a nd SENSE is above V  $_{IT} + V _{HYS}$  (the threshold hysteresis),  $\overline{RESET}$  will be driv en to a logic high after a re set delay tim e. The re set delay time is programmable by C  $_{DELAY}$  pin. Due to the finite impedance of  $\overline{RESET}$  pin, th e pull up resistor should be bigger than  $10k\Omega$ .

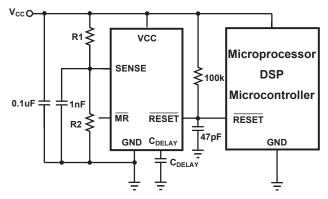

### **Monitor a Voltage**

The SENSE input pin is conn ected to the monitored system volta ge directly or through a resistor network (on MPQ6400DG-01). When the voltage on the pin is below V<sub>IT</sub>,  $\overrightarrow{\text{RESET}}$  is asserted. A threshold hysteresis will prevent the chip from responding perturbation on SENSE pin. A 1nF to 10nF bypass capacitor should be put on this pin to increase its im munity to noise. A t ypical application of the M PQ6400DG-01 is shown in Figure 4. T wo external resistor s form a voltage

divider from m onitored voltage to GND. Its tap connects to the SENSE pin. The circuit can be used to monitor any voltage higher than 0.4V.

### Figure 4—MPQ6400DG-01 Monitoring a User-Defined Voltage

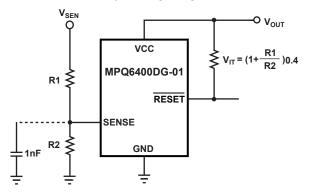

#### Monitor Multiple System Voltages

The m anual reset ( $\overline{\text{MR}}$ ) can introduce another logic signal to control the RESET. When  $\overline{\text{MR}}$  is a logic low (0.25V<sub>CC</sub>), RESET will be asserted. After both SENSE and  $\overline{\text{MR}}$  are above their thresholds, RESET will be driven to a lo gic high after a reset delay time. The  $\overline{\text{MR}}$  is internally connected to V<sub>CC</sub> through a 90k $\Omega$  resistor so this pin can float. See how multiple system voltages are monitored by  $\overline{\text{MR}}$  in Figure 5. If the signal on  $\overline{\text{MR}}$  isn't up to V<sub>CC</sub>, there will be an additional current through internal 90k $\Omega$  pull u p resistor. A logic-level FET can be used to minimize the leakage, as shown in Figure 6.

Figure 5— MPQ6400 Family Monitoring Multiple System Voltages

Figure 6—Minimizing  $I_{cc}$  When  $\overline{MR}$  Signal isn't over Vcc by External MOSFET

#### **Programmable Reset Delay Time**

The reset delay tim e can be programmed by  $C_{DELAY}$  configure. When  $C_{DELAY}$  is connected to VCC through a resistor between 50k  $\Omega$  and 200k $\Omega$ , the delay tim e is 380m s. When  $C_{DELAY}$  floated, the delay tim e is 24m s. In addition, a capacitor connected C  $_{DELAY}$  to GND could be used to get the user's program mable delay time from 2.1ms to 10s. The three configures can be found in Figure 7(a)(b)(c).

# Figure 7—Programmable Configurations to the Reset Delay Time

The external capacitor  $C_{DELAY}$  must be larger than 150pF. For a given d elay tim e, the capacito r value can be calculated using the followin g equation:

$C_{\text{DELAY}}(nF) = [t_{\text{D}}(s) - 4.99 \times 10^{-4}(s)] \times 107$

The reset delay time is determined by the charge time of external capacitor. While SENSE is above  $V_{IT}$  and  $\overline{MR}$  is a logic hig h, the internal 140nA current source is enabled and star ts to charg e the capacitor to set the delay time. When the capacitor voltage rises to 1.13V, the  $\overline{RESET}$  is deasserted. The capacitor will be discharged when the  $\overline{RESET}$  is again asserted. Stray capacitance may cause errors of the delay time. A ceram ic capacitor with low leakage is strongly recommended.

## **SENSE Voltage Transients Immunity**

The M PQ6400 can be immune to SENSE pin short negative transient. The m aximum immune duration is 17us while overdrive is 5%. A shorter negative transient can not assert the RESEToutput. The effective d uration is r elative to t he threshold overdrive, as shown in Figure 8.

SENSE THRESHOLD OVERDRIVE(%) Figure 8—Maximum Transient Duration vs. Sense Threshold Overdrive Voltage

## **PACKAGE INFORMATION**

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Int ellectual Property rights are n ot infringed u pon when integrating MPS product s into any application. MPS w ill not assume any legal responsibility for any said applications.